"메모리반도체 산업에서 첨단 패키징 기술 중요성 높아져"

"메모리반도체 시장이 고도화될 수록 패키징의 역할이 더욱 중요해지고 있다. 이에 차세대 메모리반도체 시장에서는 D램에 3D 스태킹 기술이, 낸드플래시에는 웨이퍼 본딩 기술이 적용될 것으로 전망한다"

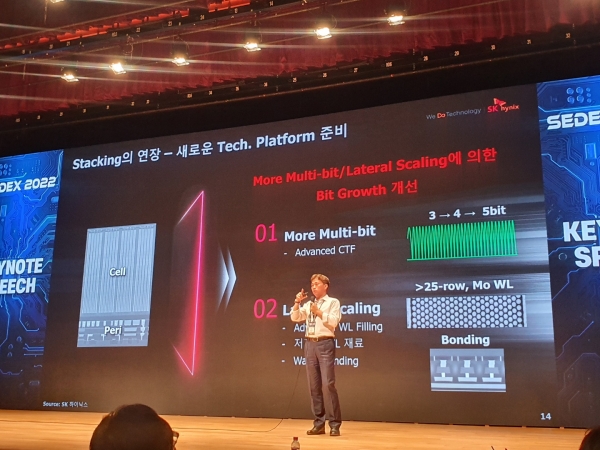

곽노정 SK하이닉스 대표는 5일 서울 코엑스에서 열린 '반도체대전(SEDEX) 2022'에 기조연설에서 향후 메모리반도체 패키징 기술에 대해 이같이 밝혔다.

SEDEX는 반도체 생태계 관련업체들의 첨단 제품 및 기술을 소개하는 종합전시회다. 이날 기조연설은 곽노정 SK하이닉스 대표가 '메모리 기술의 한계를 넘어'를 주제로, 김형준 차세대지능형반도체사업단 단장이 '반도체 초격차 경쟁력을 위한 패키지 선도 전략'을 주제로 각각 발표했다.

곽노정 SK하이닉스 대표는 "D램, 낸드플래시 등 메모리반도체가 지속적인 스케일링(공정 미세화)을 추구하고 있으나, 10나노대 1d 세대에 접어들면 기존 기술로는 트랜지스터 선폭을 줄이는 데 한계에 부딪힐 것"이라며 "이에 따라 High-NA, High-K 등 다양한 기술이 도입되고 있다"고 설명했다.

곽노정 대표는 이어 "특히 차세대 메모리반도체인 HBM, 고적층 낸드플래시 개발을 가능케하는 패키징 기술의 역할이 더욱 중요해지고 있다"며 "향후에는 D램에 스태킹 기술이, 낸드플래시에는 웨이퍼 본딩 기술이 도입될 것"이라고 덧붙였다.

D램 스태킹은 현존하는 3D 낸드플래시와 비슷하게, D램을 눕힌 채로 적층하는 기술이다. 기존 평면에 배치된 트랜지스터를 여러 층으로 쌓아 공간효율성을 높일 수 있다. 웨이퍼 본딩은 웨이퍼와 다이, 혹은 웨이퍼와 웨이퍼를 접합하는 패키징 기술로, 단일 웨이퍼가 가진 물성의 제약을 뛰어넘어 다양한 특성을 구현할 수 있다는 장점이 있다.

김형준 차세대지능형반도체사업단 단장은 패키징 기술 및 경쟁력 강화의 중요성을 강조했다. 김형준 단장은 "주요 반도체 업체들이 3D 스태킹, 이종집적 등 첨단 패키징 기술 개발에 막대한 투자를 진행하면서 관련 시장의 성장률은 매우 높게 전망되는 상황"이라며 "다만 국내 OSAT 업체들은 아직 시장에서의 점유율이 높지 않고, 투자 여력이 부족해 국가적 지원이 필요하다"고 설명했다.

김형준 단장이 제안한 국내 패키징 기술력 강화 전략은 크게 기술별 한계 돌파형 R&D 추진, 산학연 상생협력 생태계 조성, 반도체 패키징 전문인력 양성 등으로 나뉜다. 이들 사업은 국내 차세대 패키징과 관련한 산학연 단체를 조성하고, 협업 플랫폼 구축 및 패키징 전문 교육 프로그램 개발 등을 주 골자로 한다.