삼성전자가 극자외선(EUV) 기반 7나노미터(㎚·10억분의 1m) 시스템반도체를 실리콘관통전극(TSV) 공법으로 3단 적층하는 기술을 개발했다.

삼성전자는 13일 EUV 공정을 거친 반도체 칩 등을 3차원(3D) 형태로 쌓아 올리는 패키지 기술인 '엑스큐브(X-Cube:eXtended-Cube)를 적용, 테스트 칩을 생산했다고 밝혔다. 7나노 이하 EUV 공정에 TSV를 적용한 건 삼성전자가 반도체 업계 중 최초다.

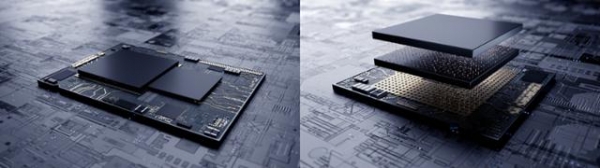

엑스큐브는 전 공정을 마친 두 개 이상의 칩을 얇게 쌓아 올려 하나의 반도체로 만드는 후 공정(패키징) 기술이다. 일반 시스템반도체는 중앙처리장치(CPU)·그래픽처리장치(GPU) 역할을 하는 로직(연산) 칩 옆에 캐시메모리(임시저장장치) 역할을 하는 S램을 붙여 2차원으로 형태로 설계한다. 엑스큐브는 S램을 로직 칩 위에 3D 형태로 쌓아올린다. 나란히 배치하는 형태가 아니기 때문에 마더보드에 닿는 칩 면적이 줄어든다. 이처럼 면적을 줄이면 보다 큰 배터리를 적용할 수 있어 제품을 더 오래 쓸 수 있다.

TSV를 활용했기 때문에 처리 속도와 전력 효율도 높다. TSV는 위 아래 칩 가운데에 뚫린 수천 개의 미세한 구멍을 전극으로 연결, 이를 통해 데이터를 주고받는다. 통로가 수천 개이기 때문에 대량으로 데이터를 전송할 수 있다.

강문수 삼성전자 파운드리사업부 마켓전략팀 전무는 "EUV 장비가 적용된 첨단 공정에서도 TSV 기술을 안정적으로 구현한 데 의의가 있다"며 "반도체 성능 한계 극복을 위한 기술을 지속적으로 혁신하겠다"고 말했다.