편집자 주 : 전자부품 전문미디어 디일렉은 미국 메모리 반도체 전문 시장조사업체 오브젝티브 애널리시스(OA:Objective Analysis)와 콘텐츠 및 리서치 데이터를 국내에 단독으로 공급하는 계약을 체결했습니다. 주기적으로 오브젝티브 애널리시스가 제시하는 메모리 시장 통찰력을 제공해드리겠습니다. 오브젝티브 애널리시스 대표인 짐 핸디(Jim Handy)는 내셔널세미컨덕터, 인텔, IDT에서 경험을 쌓은 후 1991년부터 2000년까지 데이터퀘스트(현 가트너) 애널리스트, 세미코리서치 이사 등을 역임한 인물입니다. OA로부터 추가로 통찰력을 얻고 싶으시다면 thelec@thelec.kr 로 메일을 주십시오.

지난 3월 25일. 삼성전자는 "처음으로 (1x나노) D램 생산에 극자외선(EUV) 공정을 채택했다"고 공식 밝혔다. 약 1년 전 (미국에서) 비슷한 소문이 있었는데, 삼성전자가 이를 공식 인정한 것이다.

그렇다면, 다른 메모리 기업(마이크론)은 왜 D램 생산에 EUV를 쓰지 않는 것일까?

마이크론 기술 개발 담당 부사장인 스콧 디보어는 작년 5월 기술 로드맵과 전략을 제시하는 웹캐스트에서 현재 공개된 마지막 D램 프로세스 노드 직전(1y나노)까지 EUV를 사용하지 않는 이유를 설명했었다.

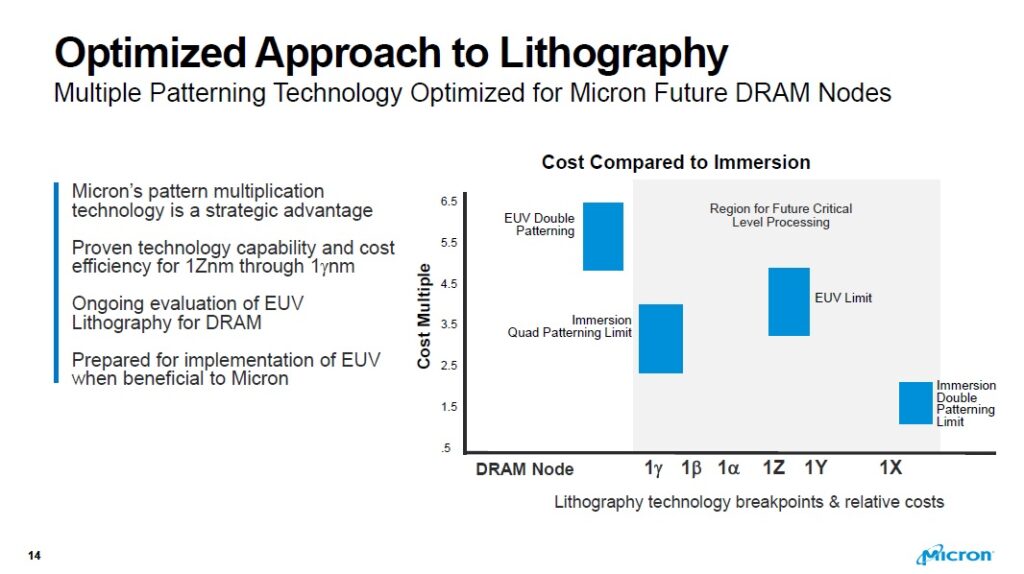

위 슬라이드는 D램 생산 공정에 따른 소요 비용을 마이크론이 비교해 제시한 것이다. 보다 진보한 공정이 축 왼쪽이다. 오른쪽으로 갈수록 오래된 공정이다(편집자 주. 그래프가 아래로 갈수록 비용은 낮아지고, 위로 가면 높아집니다. 최신 공정일수록 비용이 증가합니다). 슬라이드 왼쪽 아래에는 "마이크론에 이익이 될 경우 EUV 적용 가능(Prepared for implementation of EUV when beneficial to Micron)"이라는 문구를 적어 놨다. 마이크론 역시 EUV 적용을 염두에 두고 있으나, 1y나노 공정 이후에나 고려할 것이라는 의미로 해석할 수 있다.

마이크론은 193nm 광학 리소그래피(이머전 ArF)와 더블 패터닝 기법을 유지해 EUV 공정 적용을 뒤로 늦추고 있다. 슬라이드를 자세히 살펴보면 1z나노 노드를 지나 EUV가 도입된 상황에서도 멀티패터닝이 필요하다는 점을 알 수 있다. 삼성전자는 "EUV 기술 도입으로 멀티 패터닝으로 야기되는 반복 과정을 줄일 수 있다"고 주장했다. 이 주장은 1x에서 1z나노 공정까지만 해당되는 이야기다(편집자 주. EUV 역시 추후 미세화 과정에서 멀티패터닝이 필요하다는 의미입니다).

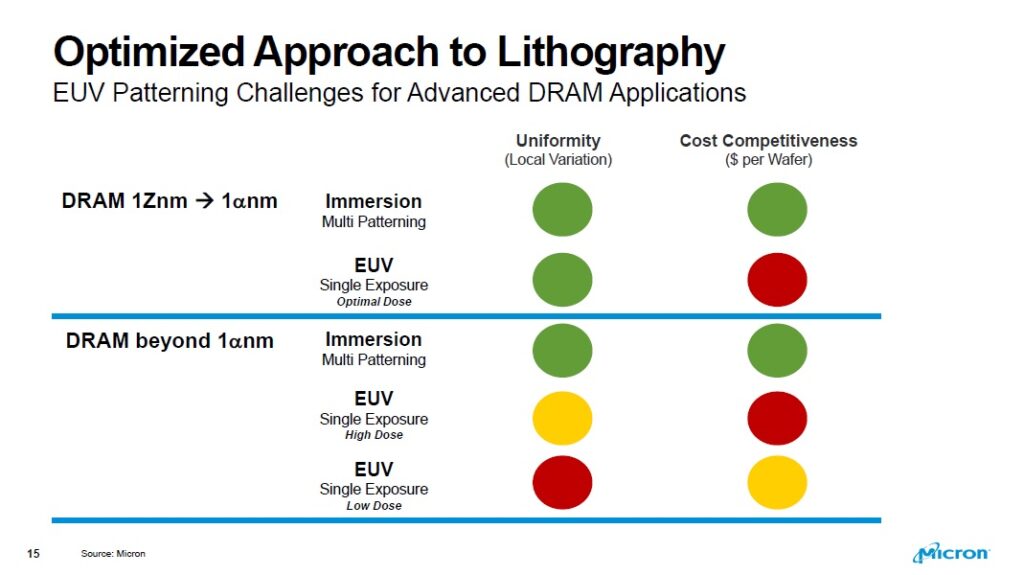

디보어는 (자사 관점에서) 1α나노 혹은 그 이하 공정에서 EUV보다 이머전 광학 리소그래피가 더 효과적이라고 주장했다. EUV가 1z나노와 1α나노 공정에서 좋은 균일성을 보장(수율이 좋을 것이라는 의미)하지만 그와 동시에 원가 경쟁력은 떨어진다는 분석을 내놓고 있다. 1α나노 이하 공정에선 어떠한 경우라도 EUV의 웨이퍼당 생산 단가가 이머전보다 낮을 수 없다고 주장했다. 오히려 수율의 경우 이머전 멀티패터닝이 EUV 대비 높다는 식으로 표기했다.

그렇다면 삼성전자는 왜 EUV가 효율적이라고 말할까?

삼성전자는 파운드리 사업을 함께 하고 있다. EUV는 통상 10나노 이하 CMOS 로직 공정에 필요하다. 삼성은 이미 7나노 파운드리 웨이퍼 생산을 시작한 상태다. 삼성전자는 파운드리 사업을 위해 EUV 장비를 대량 구비했다. 이렇게 도입한 장비 일부를 D램 생산에 활용할 수 있다. 장비 도입 비용을 유의미한 수준으로 절감할 수 있다.

마이크론과 SK하이닉스는 첨단 파운드리 사업을 하지 않고 있다. 오로지 D램 전용으로 EUV 장비를 구입해야 한다. 경제적으로 따지면 수지가 맞지 않는다. 따라서 삼성을 제외한 D램 생산기업은 EUV에 쉽게 손을 댈 수 없다. 단순히 1~2개 레이어에 EUV를 공정을 적용하기 위해 관련 장비를 구매할 수 없다는 의미다. EUV로의 전환은 엄청난 비용을 요구한다. 삼성 외 메모리 기업은 EUV를 재빨리 도입해야 할 대상이 아니라 '최대한 늦추거나 피해야할 대상'으로 여기고 있다.

한 가지 덧붙이고 싶은 얘기도 있다. 삼성전자는 1x나노 D램에 EUV를 적용했다고 밝히면서 모듈 100만개를 출하했다고 밝혔다. 얼핏 많은 숫자처럼 보이지만, 그렇지는 않다. 100만개 모듈이라면 칩 개수는 800만개 정도 된다. 일반적으로 300mm 웨이퍼 한 장에선 칩(Die)당 면적이 60제곱밀리미터(mm2)일 때 1000개 정도를 뽑아낼 수 있다. 이 수치를 대입하면 800만개 칩은 웨이퍼 8000장에서 나온 수치다. 일반적으로 D램 웨이퍼 제조공장 한 라인은 월 6~7만장 웨이퍼를 생산한다. 8000장 웨이퍼는 일반적 생산 라인에서 4일이면 생산할 수 있는 양이다.

SSD는 DRAM보다 미세화가 느린가요..?

왜 SSD에는 EUV공정을 적용하지 않아요?