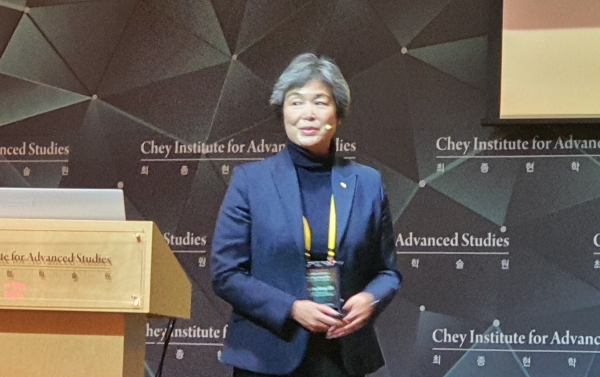

수재 킹 류 UC버클리 공과대학 교수는 지난 10일 서울 강남구 한국고등교육재단에서 열린 '최종현학술원 과학혁신컨퍼런스'에서 "컴퓨팅 성능 개선을 위해 재료, 트랜지스터, 스위치, 아키텍쳐 등 모두가 공동으로 협업하는 '코(Co)-디자인'을 해야 한다"고 말했다. 트랜지스터 집적도 확대 만으로는 컴퓨팅 성능 개선이 점차 어려워지는 상황을 해결하고 그는 설명했다.

수재 킹 류 교수는 UCLA, 시놉시스를 거쳐 현재 UC버클리대학에서 공과대학 학장을 맡고있는 반도체 분야 석학이다.

류 교수는 "현재 트랜지스터 설계, 컴퓨터 아키텍처, 소프트웨어 엔지니어 등 각 계층별로 분업이 이뤄지고 있다"며 "트랜지스터 스케일링만 하기보단 여러 계층을 아우르는 코-디자인을 통해 반도체 퍼포먼스와 효율성을 개선해야 한다"고 했다.

이날 행사의 또 다른 강연자인 위구연 하버드대학 석좌교수는 "상보형금속산화반도체(CMOS) 성능 성장이 점차 완만해지고 있지만 아직까지 뒤를 이를 킬러 기술이 등장하지 않았다"며 "업계는 병렬화와 특화를 통해 성능개선을 이뤄가야 한다"고 말했다.

위 교수는 지난해 삼성리서치 '펠로우'로 임명돼 인공신경망 기반 차세대 프로세서 연구를 맡았다. 2002년부터 하버드대학 전기공학과와 컴퓨터과학과 교수로 재직하고 있다. 병렬화는 하나의 태스크를 나눠 병렬식으로 동시에 처리하는 것을 말한다. 특화는 사용 목적에 맞게 필요한 컴퓨팅 성능을 끌어 올리고, 그로 인해 일부 성능은 포기하는 개념이다.

위 교수는 "누구 하나가 주도해서 전 분야에 걸쳐 코-디자인을 주도하기에는 각 특성이 너무나 달라 당장은 어려운 얘기일 수 있다"며 "그러나 코-디자인을 통해 목적에 맞게 성능을 최적화한다면 보다 컴퓨팅 성능을 향상시킬 수 있을 것"이라고 했다.

최종현학술원은 고(故) 최종현 SK 선대회장 20주기를 맞아 설립됐다. SK하이닉스와 SK이노베이션을 보유한 SK는 '배터리부터 반도체까지'를 주제로 컨퍼런스를 진행했다. 올해로 2회째 열린 행사다.