반도체 파운드리 시장 재진출을 선언한 인텔이 패키지 기술을 무기로 꺼내들었다.

전공정과 후공정 패키지 서비스를 일괄 제공하거나, 전공정 웨이퍼 가공은 다른 파운드리(TSMC, 삼성전자, 글로벌파운드리 등)가 맡더라도 자제 보유한 첨단 패키지 서비스만을 제공할 수도 있다는 계획을 밝혔다. 전문가들은 인텔이 전문 외주반도체패키지테스트(OSAT:Outsourced Semiconductor Assembly and Test) 시장, 그 중에서도 어드밴스드 패키지 서비스 분야로 영역을 확장하려 한다는 메시지로 해석한다.

톰 러커 인텔 어셈블리 테스트 부문장(부사장)은 지난 18일 온라인으로 열린 패키징 기술 브리핑 자리에서 "(팹리스는 인텔을 통해) 설계, 웨이퍼 제조, 패키징, 테스트까지 모든 서비스를 받을 수도 있고, 다른 파운드리 제조사로부터 웨이퍼를 공급받아 인텔의 패키징 서비스만 사용할 수도 있다"고 말했다.

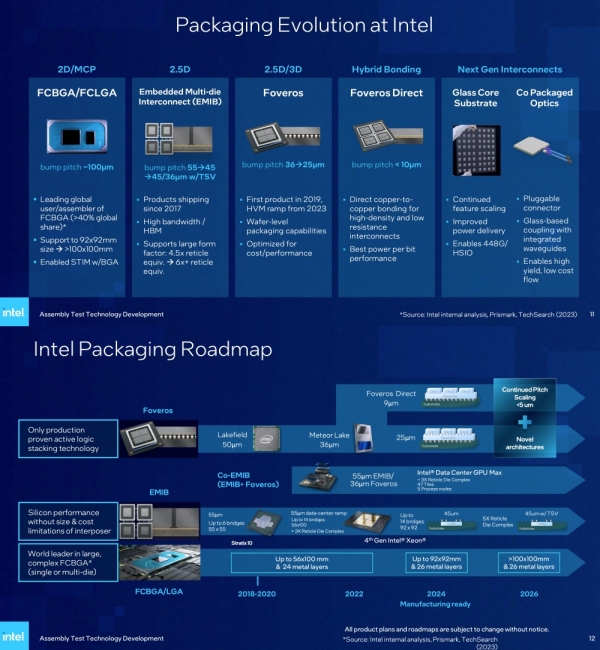

그간 자체 칩 생산 만을 해왔던 인텔은 패키지 기술도 다량 보유하고 있다. 인텔은 멀티칩패키지(MCP)에 플립칩-볼그리드어레이(FC-BGA) 기술을 활용한다. FC-BGA는 둥그런 돌기 모양 범프(Bump)가 칩 다이(Die)와 기판을 전기적으로 연결, 접합하는 형태다. 범프를 활용하면 기존 와이어본딩(wire-bonding) 방식 대비 사이즈가 작은데다 접합 거리가 짧아 외부 노이즈와 인덕턴스(inductance)도 낮다. 와이어본딩과 비교하면 입출력(IO) 속도가 빠른 것도 특징이다. 이 때문에 FC-BGA 방식을 사용하는 칩 수요는 계속적으로 늘어나고 있다. 인텔은 현재 100마이크로미터(㎛) 범프 간격(pitch)을 추후 90㎛로 축소할 계획이라고 밝혔다. 범프 간격이 줄어든다는 것은 범프 크기 축소, 패키지 내에서 더 많은 입출력(IO)을 지원할 수 있다는 의미다. 성능이 좋아진다는 얘기다.

또 다른 솔루션은 임베디드멀티다이브릿지(EMIB) 기술이다. 업계에선 2.5D 패키징 기술이라 부른다. 현재 범프 간격이 55㎛, 45㎛인 제품을 양산 중이다. 최신 서버용 중앙처리장치(CPU)인 4세대 제온 스케일러블 프로세서에 EMIB 기술이 적용돼 있다. 이 기술은 복수의 칩 다이를 기판 위에 올려서 물리 전기적으로 연결, 집적도를 높인다. 4세대 제온 스케일러블 프로세서는 최대 4개의 칩 다이를 연결해 최대 60개의 CPU 코어를 갖추고 있다.

인텔 포베로스 기술은 현 시점에선 가장 진보한 패키징 기법이다. 실리콘 칩 다이 위에 또 다른 칩 다이를 적층 패키징 하는 기술로 2019년 처음 출시된 모바일 프로세서 레이크필드에 첫 적용됐다. 당시 범프 간격은 50㎛였다. 현재 양산되는 2세대급 포베로스 기술은 36㎛, 내년에는 25㎛급으로 범프 간격을 좁힐 예정이라고 인텔은 밝혔다. 다이렉트 본딩 혹은 하이브리드 본딩 기술로 불리는 포베로스 다이렉트 기술은 구리와 구리를 직접 접합하는 기술이다. 둥근 돌기 모양 범프나 구리 기둥 모양 범프 없이 구리와 구리를 플라즈마 기술을 활용, 공유결합(covalent bond)해서 붙인다. 범프가 없기 때문에 IO를 담당하는 영역간 간격을 10㎛ 이하로 줄일 수 있다. 거리가 가까워져서 속도도 빠르고 전력 효율도 높아진다.

인텔 포베로스 다이렉트 기술은 이미 대만 TSMC가 CoWoS(Chip on Wafer on Substrate)라는 기술 명칭으로 상용화를 한 상태다. 3D V캐시 명칭(X3D)이 붙은 AMD 신규 CPU 라이젠 시리즈가 결과물이다. L3 캐시를 별도 칩으로 만들어서 CPU 위로 붙였고, 이를 통해 용량 및 전력 성능 효율성을 높인 것으로 평가받는다.

인텔은 EMIB와 포베로스 기술을 결합한 패키지 기술도 양산 중이다. 데이터센터용 그래픽처리장치(GPU)인 맥스가 주인공. 이 제품은 5개의 프로세스 노드를 사용하는 복수 칩을 적층하고, 수평으로 칩을 타일처럼 깔아서 성능을 높인 형태다. 인텔은 이날 2020년대 후반에 인쇄회로기판(PCB)이 아닌 유리를 패키지 기판으로 활용한다는 계획도 밝혔다. 유리는 무선주파수(RF)에 대한 특성이 좋은 것으로 알려졌다. SKC의 자회사 앱솔릭스가 현재 반도체용 유리기판을 사업화하기 위해 준비 중이다.

톰 러커 부사장은 "FCBGA와 2.5D 시장 자료를 보면 인텔은 이미 상당한 점유율을 확보하고 있고, 다양한 양산 경험을 했다"면서 "시스코나 AWS 등 전 세계 가장 큰 10대 패키징 고객 중 7곳과 일하고 있다"고 기술력을 강조했다.

업계 관계자는 "인텔이 파운드리 사업 본격화를 위해 패키징 기술력을 강조하는 모양새"라면서 "TSMC가 InFO(Integrated Fan Out), CoWoS 기술을 턴키로 묶어서 주요 고객사에 제공하고 있는 상황을 벤치마킹한 것이 아니겠느냐"고 했다.

디일렉=한주엽 기자 powerusr@thelec.kr

《반도체·디스플레이·배터리·자동차전장·ICT부품 분야 전문미디어 디일렉》