SK하이닉스가 차세대 메모리인 상변화메모리(P램)에 4D 낸드플래시와 동일한 PUC(Peri Under Cell) 기술을 적용한다고 밝혔다.

SK하이닉스는 낸드와 D램의 장점을 지닌 P램을 활용해 데이터센터 시장을 공략할 예정이다. 지난해 11월 인텔이 SK하이닉스에게 낸드 사업 매각시, 옵테인은 제외한 이유도 데이터센터 사업을 지속하기 위해서다. 옵테인은 P램 기술에 기반한 메모리다.

3일 세미콘코리아 컨퍼런스에서 이형동 SK하이닉스 TL은 "P램에 PUC와 알고리즘을 적용해 성능과 비용면에서 스토리지 클래스 메모리(SCM)의 요구 사항을 충족시켰다"라고 설명했다. "P램 기술은 비용과 밀도, 메모리 용량면에서 전보다 경쟁력을 갖게됐다"며 "데이터센터와 뉴로모픽 컴퓨팅의 메모리에 사용될 수 있다"고 설명했다.

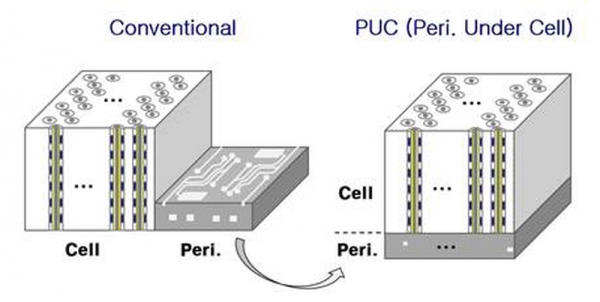

SK하이닉스가 개발 중인 P램은 PUC 방식을 사용해 메모리 용량을 대폭 늘릴 수 있을 것으로 기대된다. PUC는 기존에 셀 회로 옆에 위치하던 주변부(Peri.) 회로를 셀 회로 하단부에 배치하는 방식이다. 칩 사이즈를 줄여주고 생산효율을 높일 수 있다. 이 TL은 "P램은 10나노 공정 미만에서 저장 기반의 메모리 보다 상대적으로 측면 스케일링 제한이 적다"며 "비정질 특성으로 인해 3D 구조로 손쉽게 적층이 가능하다"고 설명했다.

P램은 PUC 뿐아니라 낸드플래시에서 활용 중인 '더블 스택(Double Stack)' 기술도 적용됐다. 적층 수가 높아짐에 따라 셀 형성을 위한 구멍을 한번에 뚫을 수가 없게되면서 두 번에 걸쳐 뚫는 방식이다. 셀을 이중으로 적층하면 단위당 셀 면적을 줄이면서도 읽기, 쓰기 성능을 높일 수 있게 된다. SK하이닉스는 P램이 향후 4스택, 6스택 기술로 확장될 것으로 전망했다.

이형동 TL은 "적층 기술을 P램에 적용하면 비트 증가, 프로세서 비용 절감, 성능 향상 등의 이점이 있다"며 "데이터 중심 컴퓨팅 시대의 전반적인 시스템 성능에 크게 기여할 것"이라고 말했다.

P램은 기존 낸드 보다 응답속도가 빠르면서, D램과 달리 주기적으로 전류를 공급하지 않아도 저장된 데이터가 지워지지 않는 비휘발성의 메모리다. 전력량에 따라 결정·비결정 상태로 바뀌는 물질을 활용해 데이터를 처리·저장한다. 반면 저항이 높고 열 간섭 문제가 발생한다는 단점이 있다.

SK하이닉스는 2012년 IBM과 협력해 P램 개발에 나섰다. 2018년에는 3D 크로스포인트 구조를 채택한 128GB P램을 국제학회 IEDM에서 발표한 바 있다.